## Embedded Binary Rewriting

## **Utilizing Ghidra and LLVM**

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### Software Engineering & Internet Computing

eingereicht von

Raphael Ludwig, BSc

Matrikelnummer 01526280

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Privatdoz. Mag.rer.soc.oec. Dipl.-Ing. Dr.techn. Edgar Weippl Mitwirkung: Dipl.-Ing. Dr.techn. Georg Merzdovnik, BSc

Wien, 1. Oktober 2021

Raphael Ludwig

Edgar Weippl

## Embedded Binary Rewriting Utilizing Ghidra and LLVM

### **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

### **Diplom-Ingenieur**

in

#### Software Engineering & Internet Computing

by

Raphael Ludwig, BSc

Registration Number 01526280

to the Faculty of Informatics

at the TU Wien

Advisor: Privatdoz. Mag.rer.soc.oec. Dipl.-Ing. Dr.techn. Edgar Weippl Assistance: Dipl.-Ing. Dr.techn. Georg Merzdovnik, BSc

Vienna, 1<sup>st</sup> October, 2021

Raphael Ludwig

Edgar Weippl

## Erklärung zur Verfassung der Arbeit

Raphael Ludwig, BSc

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 1. Oktober 2021

Raphael Ludwig

## Danksagung

An dieser Stelle möchte ich mich bei all jenen bedanken, die mich bei der Erstellung dieser Masterarbeit unterstützt und motiviert haben.

Zuerst möchte ich mich bei meinem Betreuer, Georg Merzdovnik, bedanken, der mich mit hilfreichen Anregungen und konstruktiver Kritik bei der Erstellung dieser Arbeit unterstützt hat.

Ich möchte mich auch bei meinen Studienkollegen und Freunden bedanken, die mich mit Interesse und Hilfsbereitschaft unterstützt haben. Zahlreiche interessante Diskussionen und Ideen, haben dazu beigetragen, dieses Thema in der Masterarbeit zu behandeln.

Abschließend möchte ich mich bei meinen Eltern bedanken, die mir durch ihre Unterstützung das Studium ermöglicht haben.

## Acknowledgements

At this point, I would like to thank all those who have supported and motivated me in the preparation of this master's thesis.

First of all, I would like to thank my supervisor, Georg Merzdovnik, who supported me with helpful suggestions and constructive criticism during the preparation of this thesis.

I would also like to thank my fellow students and friends who have supported me with interest and helpfulness. Numerous interesting discussions and ideas, have helped to address this topic in the master's thesis.

Finally, I would like to thank my parents, who have made my studies possible through their support.

## Kurzfassung

Eine geeignete Strategie für das Patchen und Aktualisieren von Anwendungen ist ein wesentlicher Eckpfeiler einer modernen IT-Umgebung. Während in einem Open-Source-Kontext anfällige oder veraltete Systeme leicht gepatcht werden können, ist dies bei Closed-Source-Systemen nicht der Fall. Daher kann der Einsatz von Binär-Rewriting-Frameworks als vorteilhaft angesehen werden, insbesondere bei der Untersuchung von IoT-Anwendungen, da diese Anwendungen oft Closed-Source sind.

In dieser Arbeit wurde ein Prototyp eines Binär-Rewriting-Frameworks entwickelt, um die Möglichkeiten der Nutzung von Ghidra und des LLVM-Frameworks für den Umgang mit ELF-Binärdateien und eingebetteten System-Images für ARM-Prozessoren zu untersuchen. Die Abhängigkeit von einem binären Reverse-Engineering-Framework wie Ghidra kann als vorteilhaft für die Verarbeitung von Binärdateien und eingebetteten System-Images angesehen werden, da diese Plattformen bereits verschiedene Analysatoren für unterschiedliche Architekturen bereitstellen. Allerdings ist die Umwandlung der internen Repräsentation von Ghidra (P-Code) in soliden LLVM IR-Code nicht trivial, da nicht alle Sprachkonstrukte trivial aufeinander abgebildet werden können. Daher wird in dieser Arbeit die Transformation verschiedener Sprachkonstrukte wie Phi-Knoten, Typrepräsentationen und Zeigerarithmetik diskutiert, bevor wichtige Fallstricke aufgezeigt werden, die bei der Transformation von eingebetteten Systembildern auftreten können.

Darüber hinaus wurde der Prototyp an einigen ausgewählten Binärdateien evaluiert, um zu zeigen, dass der Transformationsprozess keinen nennenswerten Laufzeit-Overhead erzeugt. Die derzeitigen Einschränkungen des Prototyp- und Transformationsprozesses, wie z. B. der Umgang mit falsch identifizierten Codeabschnitten oder Datentypen und des Neukompilierungsprozess, werden kurz anhand der Abbilder der eingebetteten Systeme Zephyr und FreeRTOS aufgezeigt.

## Abstract

A suitable strategy for patching and updating applications is an essential cornerstone of a modern IT environment. While in an open source context, vulnerable or outdated systems can be easily patched, this is not the case for closed source systems. Therefore, the use of binary rewriting frameworks can be seen as beneficial, especially when investigating IoT applications, as these applications are often closed-source.

In this work, a prototype binary rewriting framework was developed to explore the possibilities of using Ghidra and the LLVM framework to handle ELF binaries and embedded system images for ARM processors. The reliance on a binary reverse engineering framework such as Ghidra can be seen as beneficial for processing binaries and embedded system images, as these platforms already provide different analyzers for different architectures. However, transforming Ghidra's internal representation (P-code) into sound LLVM IR code is non-trivial, since not all language constructs can be trivially mapped to each other. Therefore, this thesis discusses the transformation of various language constructs such as phi-nodes, type representations, and pointer arithmetic before highlighting important pitfalls that can arise when transforming embedded system images.

Furthermore, the prototype was evaluated on a few selected binaries to highlight that the transformation process does not produce any noteworthy runtime overhead. The current limitations of the prototyping and transformation process, such as dealing with misidentified code sections or types and the build process, are briefly demonstrated using the images of the Zephyr and FreeRTOS embedded systems.

## Contents

| $\mathbf{K}$ | Kurzfassung x<br>Abstract xii |                                 |    |  |  |  |

|--------------|-------------------------------|---------------------------------|----|--|--|--|

| A            |                               |                                 |    |  |  |  |

| Co           | onten                         | $\mathbf{ts}$                   | xv |  |  |  |

| 1            | Intr                          | oduction                        | 1  |  |  |  |

|              | 1.1                           | Motivation & Problem statement  | 2  |  |  |  |

|              | 1.2                           | Theses outline                  | 2  |  |  |  |

| <b>2</b>     | Bac                           | kground                         | 3  |  |  |  |

|              | 2.1                           | ARM Architecture                | 3  |  |  |  |

|              | 2.2                           | Disassembly                     | 6  |  |  |  |

|              | 2.3                           | Ghidra                          | 8  |  |  |  |

|              | 2.4                           | LLVM                            | 11 |  |  |  |

| 3            | Stat                          | e of the art                    | 17 |  |  |  |

|              | 3.1                           | Basics of binary rewriting      | 18 |  |  |  |

|              | 3.2                           | Dynamic binary rewriter         | 19 |  |  |  |

|              | 3.3                           | Static binary rewriter          | 21 |  |  |  |

|              | 3.4                           | LLVM IR binary rewriter         | 22 |  |  |  |

| <b>4</b>     | Imp                           | lementation                     | 25 |  |  |  |

|              | 4.1                           | Type Conversion                 | 27 |  |  |  |

|              | 4.2                           | Basic Blocks                    | 29 |  |  |  |

|              | 4.3                           | Static Single Assignment form   | 32 |  |  |  |

|              | 4.4                           | Pointer arithmetic              | 34 |  |  |  |

|              | 4.5                           | Data Labels                     | 35 |  |  |  |

|              | 4.6                           | Stack                           | 37 |  |  |  |

|              | 4.7                           | Handling Varnodes               | 40 |  |  |  |

|              | 4.8                           | Special operations              | 42 |  |  |  |

|              | 4.9                           | Dynamically linked ELF binaries | 47 |  |  |  |

|              | 4.10                          | Embedded system images          | 49 |  |  |  |

|              | 4.11                          | Patch format                    | 51 |  |  |  |

xv

| <b>5</b>           | 5 Evaluation    |                   |    |  |  |  |

|--------------------|-----------------|-------------------|----|--|--|--|

|                    | 5.1             | Testing framework | 53 |  |  |  |

|                    | 5.2             | Benchmarks        | 55 |  |  |  |

|                    | 5.3             | Patching          | 59 |  |  |  |

|                    | 5.4             | Limitations       | 61 |  |  |  |

| 6                  | Cor             | nclusion          | 67 |  |  |  |

|                    | 6.1             | Future work       | 69 |  |  |  |

| $\mathbf{Li}$      | List of Figures |                   |    |  |  |  |

| $\mathbf{Li}$      | st of           | Tables            | 75 |  |  |  |

| List of Listings   |                 |                   |    |  |  |  |

| List of Algorithms |                 |                   |    |  |  |  |

| Bi                 | Bibliography    |                   |    |  |  |  |

## CHAPTER

## Introduction

Binary rewriting can be a very powerful tool when it comes to patching and updating vulnerable or outdated systems. Not only allows binary rewriting the users to modify and harden applications, but also allows them to patch applications even when no source code is available. This especially helps in situations where closed source software is vulnerable and has to be patched in some way. Past attacks [1] have shown how vulnerable and dangerous a homogenous infrastructure can be when it is freely accessible on the Internet. This does not only apply to routers, but also affects IoT and edge devices that enable other resource constraint devices to connect to the internet and offload heavy computations into the cloud. Such IoT devices often utilize a real time operating system with a TCP/IP stack to achieve this. While security critical bugs [2] in such systems have serious consequences, not all devices might be patched by the manufacturer for various reasons. One reason could be that the manufacturer simply does not support the device anymore, which means that the end user has to buy a new device or life with a potential security problem. With an appropriate binary rewriter such problems can be eliminated without relying on the manufacturer and therefore can help to create more secure environments. But not only the firmware of the devices itself should be scrutinized, because IoT devices can often be controlled with a corresponding App. Which means that the security of the Smartphone and IoT devices are strongly linked together [3]. With an appropriate binary rewriter that focuses on firmware images of embedded systems and the ARM architecture, these problems can be managed to a certain extent and thus contribute to a safer environment. Nevertheless, there are many problems that are introduced when rewriting a binary without the source code. Because the binary has to be analyzed first, such a rewriting process is more complex than rewriting a program where the source code is available. Not only is it difficult to reconstruct the control flow from binaries, but also reconstructing the different data types that have been used throughout the program is not trivial [4].

#### 1.1 Motivation & Problem statement

While the majority of binary rewriters focuses on the x86 instruction set, some binary rewriters for ARM also exist. But currently there are no IoT specific binary rewriters that can process firmware images. Although the ARM instruction set is not as complex as the x86 instruction set, most binary rewriters focus on the latter. Because the x86 instruction set uses variable length instructions, the binary rewriter has sometimes more options to transform the code, but decompiling and analyzing can be harder than with ARM. However, the ARM instruction set offers additional challenges that must be solved in order to rewrite binaries with minimal computing and space overhead. Embedded devices are often restricted, not only by processing power, but also by storage and memory, binary rewriters that target such platforms must take these limitations into consideration. Often the overhead that is introduced by binary rewriters renders most of the transformed binaries unusable for such resource constraint devices like a router or an IoT edge device. Because when rewriting a binary, the changes usually cannot be applied in place, which means that the resulting binary will naturally either grow or shrink, the binary rewriter must take this into account and also correct the relative and absolute jump addresses of the affected regions. In addition to direct manipulating of the assembly, there are also other ways to transform the binary by using an intermediate representation language in which the binary is lifted before analysis and can then also be compiled from it [5]. Although there are many such intermediate representation languages [6] used by software analyzing tools, not many binary rewriters utilize existing ones, but create their own internal ones for analyzing. The transformation process is then most of the time done directly at the assembly level without the help of a compiler that could try to reduce the overhead of such a transformation by applying optimizations.

#### 1.2 Theses outline

The outline of the thesis is as follows. Chapter 2 will discuss background knowledge on various topics, such as the ARM architecture, Ghidra, and LLVM, to provide a brief introduction to topics that are relevant for binary rewriting. The next chapter 3 will cover the current state of the art of binary rewriters and highlight the differences between static and dynamic binary rewriters. Subsequently, chapter 4 discusses how to implement a transformation from P-Code to LLVM IR to create a binary rewriter that can export LLVM IR code using Ghidra. Not only is the transformation process of P-code operations and their structure discussed, but also how dynamically linked binaries or embedded system images can be handled in such a transformation. In chapter 5, this implementation is evaluated for both correctness and performance while discussing the discovered limitations of the developed prototype. Additionally, the process of using the developed prototype to patch a vulnerable program is highlighted. Finally, in chapter 6, the results of this thesis are summarized and further opportunities for research are discussed, as well as an outlook on various problems that were not addressed in this thesis.

# CHAPTER 2

## Background

This chapter focuses on highlighting various topics that will be needed throughout the thesis, such as the basics of ARM architecture and basic knowledge about disassembly. In addition, an overview of the technologies used in this work is given and important aspects of P-Code and LLVM IR are summarized.

#### 2.1 ARM Architecture

Compared to the x86/x86-64 instruction set, which is present on processors that are mainly used for personal computers and servers, the ARM architecture is often found in mobile and embedded systems. To support not only phones or personal computers, but also low-power devices, ARM processors can implement various features that change the way these processors can handle data and code. For example, low power processors such as Cortex-M processors may only support the Thumb instruction set, while Cortex-A processors support the full AArch64 feature set and are capable of performing not only floating-point operations, but is also capable of performing simple cryptographic primitives such as hashing and en/decrypting data [7]. Such features are documented as a set of architectural profiles. For ARMv7 three such profile exist [7]:

- **ARMv7-A**: The ARMv7-A profile does support both Arm and Thumb instruction sets and requires the support of virtual addresses in the memory management model.

- **ARMv7-R**: ARMv7-R is the real-time profile, which also supports Arm and Thumb instruction sets, but does not require the support of virtual addresses.

- **ARMv7-M**: ARMv7-M is the profile for micro-controller and only has to support the Thumb instruction set. For this profile deterministic performance and a rather small size is important, as these processors are often used in low power devices.

Since the thesis focuses on embedded systems, further sections will only take the architectural profiles for micro-controller into account.

#### 2.1.1 Registers

An ARM core contains a list of general purpose and special purpose registers. Unlike x86, where a full 32-bit register (EAX) can share its memory space with the respective smaller ones (AX, AL, AH), such a behavior is not possible in a register of an ARMv7-M processor. However, the AArch64 architecture has similar functionality. ARM processors have thirteen general purpose registers, labeled from r0 to r12. These registers have a fixed width of 32 bits. Besides these registers there are also some special purpose registers that fulfill a special role [7]:

- **SP**: The SP register, also known as Stack Pointer, is used to point to the stack of the program that is currently executed. Sometimes it is also named R13. Depending on which mode the processor is currently in, the register can represent the main stack pointer (MSP) or the process stack pointer (PSP).

- LR: The Link Register, which can also be referred as R14, is used to store the return address of a branching instruction. If this register is not used, it can also be used for other purposes.

- **PC**: The PC register contains the Program Counter of the application. The value of the register is the location of the current instruction plus 4 bytes.

In addition, there are various control and co-processor registers that can be used for floating point operations or other special operations that the ARM processor does not support. Depending on the processor used, it is also possible that other registers are banked in addition to the stack pointer, which means that the register is present multiple times on the processor and the current processor mode determines which version of the register is used [7].

#### 2.1.2 Endianness

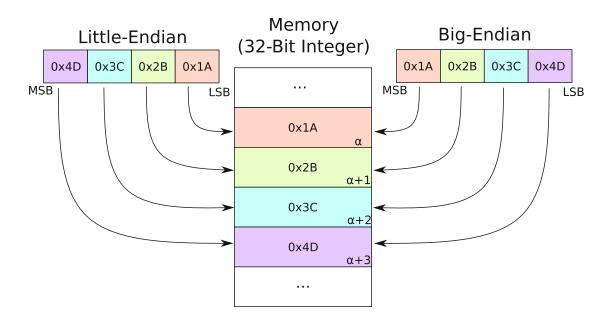

The Endianness of a processor specifies how data that is read from memory is interpreted. Most processors are either using big-endian or little-endian. As shown in Figure 2.1 the most significant byte is stored at the smallest memory address, while the least significant byte will be stored at the largest memory address. In little-endian the stored bytes are reversed, which means that the least significant byte will be stored at the smallest and the most significant byte will be stored at the largest memory address. ARM processors can support the functionality to switch from little-endian to big-endian when reading data bytes from the system memory. Instruction fetches, as well as access to control registers or the system control space are accessed with the little-endian memory system [7]. As shown in Figure 2.1, switching the endianness can result in errors when interpreting data that is

Figure 2.1: Endianness

located at an address  $\alpha$ . In this example a single 32-bit integer is located at the address, which consists of 4 successive bytes (0x1A, 0x2B, 0x3C, 0x4E). When changing from little-endian to big-endian the value of this 32-bit integer changes completely and therefore it is important to take the endianness of the memory in account when accessing special memory regions, such as the system control space region.

#### 2.1.3 Memory model

ARM processors use a rather relaxed memory model when compared to x86 processors. In this memory model hardware threads can execute load and store instructions out of order and therefore explicit synchronization mechanisms are needed to ensure consistency over all hardware threads when a single memory region is accessed. These synchronization mechanisms are data and instruction barriers, which ensure that no instruction after the barrier will be executed until all instructions before the barrier have been processed [8]. Besides a relaxed memory model, ARM processors do not restrict the type of stack that can be used by programs. It is possible to configure the type to be either full descending, full ascending, empty descending or empty ascending. But usually, full descending stacks will be generated by compilers. Although in most cases descending stacks are created, when working with embedded systems it is important to pay attention to the type of stack, since the direction of growth can not only vary, but also affect the placement of various memory segments when the binary is recompiled. Furthermore, memory that contains ARM or Thumb instructions must be aligned properly, otherwise the processor cannot correctly execute these instructions. ARM instructions are 32-bit aligned, while Thumb instructions are 16-Bit aligned [7].

#### 2.2 Disassembly

During the disassembly of a binary file, the instructions are decoded and separated from the data in the binary file. For this, two different approaches can be used and even combined to achieve better results. The first approach is known as liner disassembly, which can be seen as simpler than the recursive disassembly approach, because the file will be scanned linearly from a starting position to an ending position and all data in between will be processed. Although, this approach is rather simple, it also has its disadvantages, because if a data region is encountered that can also be interpreted as valid instructions, the resulting disassembly may not be correct. The recursive approach however, is more complex, but does not suffer from this problem, because instructions are discovered by following the control flow of the functions that are analyzed. Which means that a precise control flow graph has to be created to fully discover all functions and blocks of instructions in a binary. In addition, the recursive approach has the disadvantage that if the destinations of a jump instruction are calculated at runtime, the destinations may not be determined at all [9].

#### 2.2.1 ELF file format

The Executable and Linkable Format (ELF) file format, is a common standard for a cross-platform file format for programs and libraries that can be used by multiple operating systems. The ELF format specifies a header that includes memory segments, section headers and the data referred by these headers. Additionally, different endianness and multiple address sizes are supported to allow for flexible use [10]. When working with embedded system images, exporters are often able to export images to an ELF file format, which can then be further used in analysis tools such as Ghidra or in virtual machines (e.g. QEMU). These frameworks parse available headers and construct an environment for the program to be either analyzed or executed. For the binary analysis the sections with their respective permissions, as shown in Table 2.1, are important, because these can give hints to the framework about the intended usage of the contents. The permissions column lists the UNIX permission represent about the section, while the ELF-Type specifies the type of the section in the ELF file. SHT\_NOBITS means, that there are no bytes associated with the section, while SHT\_PROGBITS means that the ELF file provides the contents of the section.

| Name    | Permissions | ELF-Type     |

|---------|-------------|--------------|

| .bss    | rw-         | SHT_NOBITS   |

| .data   | rw-         | SHT_PROGBITS |

| .rodata | r           | SHT_PROGBITS |

| .text   | r-x         | SHT_PROGBITS |

Table 2.1: Excerpt of sections in the ELF file format [10]

#### 2.2.2 Control Flow Graph

A control flow graph is a directed graph structure, as shown in Figure 2.2, that represents the control flow of functions. But also an inter-procedural control flow graph exists, which visualizes the control flow of functions rather then blocks of assembly code [11]. In a control flow graph the nodes are represented as blocks containing one or more assembly instructions, and the edges represent the destinations of direct or conditional jumps. To effectively use such a data structure for analysis, a block contains at most one branching instruction at the end of the block. Such blocks are then called basic blocks. Therefore, edges in Figure 2.2 can be colored differently depending on their type: blue (unconditional edge), green (true) or red (false) in case of a conditional jump. Such a graph cannot only be used to visualize the control flow structure, but also to group instructions together for further analysis, or be utilized by a binary rewriting prototype as described in Chapter 4.

Figure 2.2: Ghidra: Control flow graph

#### 2.3 Ghidra

Ghidra is an open-source software reverse engineering framework, which was published by the National Security Agency Research Directorate in March 2019 [12]. Besides the ability to disassemble binaries, Ghidra is also able to decompile and analyze binaries from multiple architectures and formats. With the newest release of Ghidra 10.0 [13], also an integration with a debugger is available to debug binaries directly in the reverse engineering framework. Because Ghidra features a plugin system, the functionality can be extended and new file format parsers as well as CPU targets or analyzing extensions can be easily added to help with the analysis of binaries. In order for Ghidra to provide a consistent analysis base for several different architectures, the disassembled binary program is converted to low-level P code on which the decompiler and other analyzers can operate to produce a high-level P code layer that can then be converted to pseudo-code, which is then displayed in Ghidra. This has the advantage that an algorithm for building the control flow graph, type detection, branch analysis, and other algorithms for binary analysis do not have to be implemented separately for each architecture, but only once for the low-level or high-level P-code representation. However, this also means that architecture-specific functionality and assembler instructions are abstracted or expressed differently by such a conversion.

#### 2.3.1 SLEIGH

SLEIGH can be seen as a definition language that defines how machine instruction of a specific processor architecture should be mapped to P-Code. The language was derived from SLED and extended to be capable of encoding additional information about the control flow for the decompilation step and further analysis steps for Ghidra [14]. Since SLEIGH can be used for arbitrary architectures, basic restrictions and architecture specifics like endianness, alignment and registers have to be specified before any mapping from an instruction opcode to a P-Code operation can be provided. In order to be able to specify such basic architectural features in a modular way, SLEIGH implements a simple preprocessor language that is capable of including files and evaluating simple if expressions. Preprocessor constructs like @ifdef or @ifndef behave therefore very similarly to how #ifdef is handled in a C preprocessor. Simple instructions can be defined via the mnemonic, the parameters and different restrictions, such as the bitmask of the assembly instruction, as shown in Listing 1. In this Listing a simple unconditional branching instruction b is defined with Addr24 being the parameter of the instruction, defining the target address of the jump. The rest of the definition are the conditions to ensure that the right bit pattern is matched for the instruction, which also includes to make sure that the processor is in ARM mode and the target address is defined. The body then includes the P-Code which should be generated for the detected assembly instruction [14].

8

```

:b Addr24 is $(AMODE) & cond = 14 & c2527 = 5 & L24 = 0 & Addr24

{

goto Addr24;

}

```

Listing 1: Branching instruction definition in SLEIGH

#### 2.3.2 P-Code

P-Code is a register transfer language, which features not only basic operations on integers and floats, but also operations that can impact the control flow. In Ghidra P-Code is used to represent the semantics of the underlying machine code as close as possible. All operations can have more than one input parameters, while either producing a return value or not. These input parameters or return values are named varnodes in Ghidra and cannot only represent the register or storage location, but can also contain more information from the decompiler and analyzer stages of Ghidra. Such information can be type and control flow information. While the type information is present as additional information in the high-level P-Code, it will not be present in the low-level P-Code that is displayed in Ghidra. The control flow information is provided by the decompiler only for all high-level P-Code operations in a graph structure containing all basic blocks of a function. Therefore, there is a distinction between low-level P-Code, which can be acquired by just lifting the assembly code into P-Code without any kind of analysis and the resulting high-level P-Code that is produced by the decompiler. This is important to keep in mind, because not only can some operations change during different levels of decompilation, such as CALL, CALLIND and RETURN but it is also possible that high-level P-Code operations, such as BRANCH or CBRANCH operations, inside a control flow structure can have a slightly other meaning than in their lov-level P-Code form. While a CBRANCH operation in low-level P-Code will set the program counter to a specific operation when a condition is met, the high-level version of this P-Code will actually make use of the control flow graph to represent such a change in the programs control flow by embedding this behavior into the true and false output edges of the respective block in the control flow graph. Besides these differences, there are also P-Code operations that are high-level specific operations and will not appear in low-level P-Code. Such operations can be MULTIEQUAL or INDIRECT, which have a special meaning, while not impacting the logic or the actual control flow of the program. A MULTIEQUAL operation is similar to a  $\phi$ -expression in LLVM, while a INDIRECT operation only gives an indication to all analyzers working with high-level P-Code that a particular instruction in the binary code may also affect a particular input or output variable of another P-Code operation [15].

Because there are far less P-Code operations then instructions in the ARM instruction set, one assembly instruction is most likely translated into multiple P-Code operations. Besides basic control flow operations for branching and calling functions, there are also only basic arithmetic operations and comparisons for integer or floating-point numbers of variable length. For example, the integer addition operation INT\_ADD can operate on any sized input, with the only the restriction that both inputs must have the same size. Although any input and output varnode of a P-Code operation can be either a register, or a variable in local or global scope, a varnode can also encode constants and different address spaces, which can be useful for embedded devices, where data and executable storage are separated entities [15].

#### 2.3.3 Varnode

Varnodes are used as input and output variables by P-Code operations and can therefore be considered as unit of data that these operations process and produce. Such a varnode cannot only represent a fixed constant value, but also reference variables, registers or even memory regions that span over multiple addresses if necessary. Varnodes themselves do not have a specific type, as this information is missing in low-level P-Code, but can be enhanced with higher-level types and references to symbols in high-level P-Code that can then be displayed in the decompiled C-style code in Ghidra. Because a varnode is universally usable, a lot of information is stored in varnodes, the most important properties for the binary rewriter are listed below:

- Address range: A varnode does contain at least a start address, at which the data is stored. Such an address can point to various memory spaces, such as register or normal nonvolatile memory. While a register restricts the maximum size of the varnode, this is not necessarily true, if the varnode is stored somewhere in memory. In such cases, the annotated type or the P-Code operations used are used to limit the size of the varnode. The end address is never saved into a varnode and has to be calculated from the length and the start address.

- Length of the data: As already mentioned, the length of the data in each varnode can vary depending on the usage and the contained data. In most cases the length of the varnode matches the contained data type, but this may not necessarily be true for complex data types, such as structures, because they are often split to multiple varnodes. This is necessary since not all P-Code operations can handle these data types.

- **High-Level Information**: The amount of high-level information, such as the presence of a data type, a high-level variable, or even a symbol, depends on the level at which the P-code operations were generated. In a low-level analysis these types are missing, while in a high-level analysis most varnodes contain a higher-level data type or symbol. A missing data type cannot only indicate errors in the analysis, but also be an indicator for code that might have been obfuscated.

- **Definition**: A variode also caries information about its definition, where the variode was previously modified or assigned a new value. This most of the time refers to another P-Code operation where the variode was used in the output slot,

10

but this can also be undefined if there is no logical definition of the varnode. This is often case if a varnode is a parameter of a function.

• **References of usage** Besides these properties, a varnode can also reference all P-Code operations where the varnode will be used as parameter. This can be used to analyze the flow of the data throughout the function.

#### 2.3.4 Address spaces

According to the usage, all addresses of Varnodes are assigned to address spaces in Ghidra. Such address spaces can be the normal nonvolatile memory (RAM), the stack memory region or even a constant memory space, which can be an indicator that a certain varnode can be considered a constant value and never changes throughout the execution of the program. In P-Code, there is also a unique address space that is used to mark varnodes that are not overwritten by a P-Code operation throughout their lifetime, but can have the same physical memory address as other varnodes. These address spaces can be used in the analysis step to perform different kinds of optimization and help in identifying different variables and how the data is moved within a function. Such address spaces can also be used to mirror hardware specific memory spaces, such as the separation of ROM, flash and RAM. But this is usually not the case when a binary is analyzed by Ghidra, because hardware specific information would be needed for the binary analysis step to build such address spaces.

#### 2.4 LLVM

LLVM is a powerful compiler infrastructure that does not only support multiple different backends, but also different frontends. One such fronted is for example clang, which can translate C/C++ code into the LLVM intermediate representation (IR) that is used by the compiler infrastructure to not only optimize the code, but also by the compiler backend to produce machine code for the target architecture [16]. The LLVM IR is s static single assignment (SSA) language, which is also strictly typed to ensure type safety when compiling any code into assembly instructions. With this intermediate representation it is possible to represent all high-level languages without any modifications to the language specification. This is possible because the LLVM IR provides common low-level operations that can be used to build higher-level constructions. But this also means that for some languages a transformation to this intermediate representation can be more difficult than for others [17].

While there are multiple representations of the LLVM IR, such as in-memory, on-disk bitcode (.bc) and a human readable language representation (.ll), this section will focus on the latter two representations as they are used latter on by the binary rewriting framework. Additionally, any LLVM IR code that is generated with the LLVM framework can be easily serialized into both of these representations and therefor also easily inspected and exchanged between different programs. Although the language syntax allows certain constructs, as shown in Listing 2, these expressions will later than be rejected by a verification pass, as all expressions in the LLVM IR must be well formed. In the shown example the SSA property is violated and therefore it will result in a parser error when trying to compile such code with the LLVM framework [17].

%result = add i32 %result, 1

Listing 2: Non well formed LLVM IR expression

#### 2.4.1 Static Single Assignment (SSA)

As already mentioned, the LLVM IR is a static single assignment from, which can be seen as a restrictive property of the intermediate representation [18]. Because of this property a variable must only be assigned once and cannot be used before it was defined, which makes the example shown in Listing 2 not well formed. While such a property can be limiting when transforming other languages into the LLVM IR, a SSA language can then be used to identify unused variables and can also help in allocating registers for different variables. Although a static single assignment form can easily be used for analysis and optimizations, representing local variables in a stack frame or referencing other variables from other blocks can be difficult. Therefore, LLVM IR allows for allocation of stack memory with **alloca**. While this expression yields a pointer to the allocated memory, the pointer has a type information attached to it, which must be specified in the **alloca** expression. With the help of this pointer local variables that reside on the stack can be accessed. Although referencing a single variable in another block is easily possible in a SSA language, it can get problematic in case of loops or other constructs that expect a value from the previous executed block is present. For this reason,  $\phi$ -expressions (nodes) are needed [17].

#### 2.4.2 $\phi$ -expression

In a SSA language  $\phi$ -expression (nodes) are mainly used to solve a fundamental problem when working with such representations. A variable can only be assigned once and afterwards it is not possible to change the variable in any way. Therefore, when working with loops, or pieces of code that can have multiple incoming edges in one code block, a problem arises. Namely how should these changes be propagated and how can these variables be referenced correctly. In LLVM IR such  $\phi$ -expressions must dominate all other expressions in a block and have to have a value for each incoming edge of the current block in the control flow graph. As shown in Figure 3 the variable result will reference a different value depending on the previous block. Such  $\phi$ -expression can therefore also be used to easily represent loop counters in a SSA form, because referencing, both the initial value and the value from the previous iteration is possible without reassigning a new value to the variable [17]. %result = phi i32 [ 0, %entry ], [ %next, %block1 ] Listing 3: Example \u03c6-expression

#### 2.4.3 Types

The LLVM internal representation language is a strongly statically typed language. In LLVM IR both, the declaration of a function or variable and the point of usage an appropriate type has to be specified, which will then be enforced throughout the program. In case of any type mismatches, a compilation will fail, as there are no automatic casts from on type to another, even when they would be compatible with each other. In LLVM IR variable sized integers and a number of common float representations can be considered as primitive types. When an integer type is used, the width of the integer has to be specified beforehand in the following format: i<width>, where width is the size of bits the integer should have. For example, when defining a 4-byte integer, the i32 type is used. This can be useful for handling various high-level types that either have a target specific or custom size. One such high-level type can be a boolean, which can be converted into an integer with width 1 bit (i1). Besides these also pointers, arrays and structures can be created in the type system [17].

#### 2.4.4 Global symbols

Global symbols in LLVM IR can be global variables or functions that are visible in the whole compilation unit. These symbols always have to start with an @ character and can be seen as a pointer to their storage space. In LLVM IR this is needed, because a global variable describes most of the time a region in memory that can be accessed by any function in the compilation unit. Since every memory region in LLVM IR is accessed by a pointer, a global variable should also reflect this idea. Additionally, LLVM IR is also in a value SSA form and therefore changing a value without pointers can be a complicated task. Therefore, to accessing the contents of such global symbols often requires the usage of **load** or **store**, or **call** expressions. Global variables can optionally specify different properties, such as the linkage type and properties such as unnamed\_addr or local\_unnamed\_addr, which can be used by the compiler to optimize the behavior of a global variable further. For example, if unnamed\_addr is given, the compiler may merge constant values with other constant values that have similar contents, as the property signals the compiler that the address of this symbols is not relevant for the program. Global variables can also contain a property that defines the section name in which the global variable should be contained in the final binary [17].

#### 2.4.5 Functions

Functions in LLVM IR can be seen as special global symbols that point to a region of executable memory. A function in LLVM IR has to be at least declared and an external property has to be added if the function is not contained in the current compilation unit. Otherwise, a function needs an entry block, which then contains all LLVM IR expression

that should be contained in the function. Since the name of these blocks is only local to the function, multiple functions can have the same block labels without interfering with each other. A function in LLVM IR, must always have a return value, if the function should not return anything the special value **void** as to be chosen, which also signals the calling site that the respective **call** expression does not have a result that can be assigned to a variable [17].

#### 2.4.6**Intrinsic Functions**

When generating LLVM IR expressions from P-Code operations or even directly assembly code, it is possible that not all of these operations can be expressed in expressions that are available in the LLVM IR language. This can be a common case when working with code that is either highly optimized for an architecture, or a lot of builtin functions have been used by the developers or statically linked libraries in the application. One way to handle such occurrences is to rely on LLVM intrinsic functions. Most of these functions that can be applied in such cases are all platform specific and therefore produce non-portable code and should not be used directly if not really necessary. Although, most of the time intrinsic functions simply represent platform specific instructions such as strex or ldrex also other more portable intrinsic functions exist. One example for such a function would be llvm.read\_register.i32 (metadata), which allows at least in theory to read the contents of a register. Nevertheless, it can only be used to retrieve the stack pointer on certain platforms. The same restrictions can also be applied to the llvm.write\_register.i32 (metadata, i32) function, which is able to write a value to a register. In the intermediate representation such intrinsic functions behave exactly like any other normal functions and therefore also have to be declared with the right signature before they can be used [19] [17].

#### 2.4.7Inline Assembly

Not all generated assembly or P-Code constructs can be represented as normal expressions or intrinsic functions in LLVM. This can be the case for highly optimized or customized code, which cannot only be found in user space applications, but also in kernel space. Especially when working with embedded images this can be the case, because no library can be used to abstract interactions between user space and kernel space, or other processes such as handling interrupts and switching tasks or accessing hardware or platform specific registers. Such interactions usually rely on hand crafted assembly code, which is often hidden in platform specific frameworks that provide the functionality. If such constructs are encountered while the conversion between P-Code and LLVM is in process, these instructions have to be converted into inline assembly, otherwise these instructions would be missing from the final export and can therefore lead to an incomplete and wrong application. Compared to the C/C++ interface of the LLVM toolchain, the usage of inline assembly is rather limited in the LLVM IR language, because all inline assembly code has to be encoded as a function call [17]. While this still allows the usage of arbitrary assembly instructions in a controlled manner, it also

ensures through the semantic of the function call that these variables can be freely used as input parameters for an assembly instruction and that the compiler can also retrieve the return value from a register.

## %1 = call i32 asm sideeffect "mrs \$0, BASEPRI", "=r"() Listing 4: Example LLVM IR inline assembly

An example for an inline assembly function call can be seen in Listing 4. The example encodes an access to the MRS register to retrieve the base priority mask and can often be found in kernel-space code. When creating such inline assembly function calls, the keyword **sideeffect** is often used to ensure that the compiler knows that side effects can occur that are not apparent through the constraint list. This also prevents the compiler from removing the assembly in a optimization stage. In this case the LLVM IR framework does not provide any intrinsic functions for such a platform specific behavior, but since the conversion is rather trivial the binary rewriting framework can either choose to rely on other third-party library that implement such a behavior or supply a direct inline assembly call as shown in Listing 4

# CHAPTER 3

## State of the art

This chapter gives an overview of the current state of the art by summarizing important aspects of binary rewriters and highlights different approaches. Since binary rewriters must disassemble at least parts of the binary to be able to modify it, the quality of the used disassembler is very important to such rewriters. Not only dictates the disassembler which binaries the rewriter can process, but the rewriter also has to take into account that the process of disassembling a binary is not a straightforward process and depending on the compiler optimizations the disassembled binary might differ from the actual source code that should be patched accordingly [5]. Most binary rewriters that currently exist, can be grouped into the following categories: static, dynamic and hybrid. These categories not only describe the basic approach that a rewriter follows, but also makes comparing different binary rewriters with each other easier, because rewriters from different categories might choose different approaches, such that the process might not be applicable for the same problem. Although most static binary rewriters rely on a control flow graph, which is typically extracted by a decompiler, to rewrite the binary, E9Patch [20] tries to accomplish this transformation by only using control flow agnostic methods. But because these methods are based on heuristics E9Patch does not have a 100 percent coverage and the overhead that is introduced makes it not suitable for resource constraint devices. Additionally, static rewriting or patching is not always possible for some resource constrained devices that provide real-time services, a patching mechanism can take advantage of the hardware-specific characteristics of such devices to inject code that can patch the system. On embedded systems that are powered by ARM SoCs this can be done by utilizing the hardware debugging unit, which cannot only load and rewrite the current program, but can also change the control flow via hardware breakpoints [21]. Besides static and dynamic binary rewriters, which will be discusses further in Section 3.2 and Section 3.3, also hybrid binary rewriters exist. These types of rewriters utilize both rewriting methods when rewriting binaries to improve their overall success when handling complex binaries.

#### 3.1 Basics of binary rewriting

Regardless of the approach used by a binary rewriter, the key steps that such a rewriter must perform can be summarized as follows [5] [22]:

- **Parsing**: Executable binaries can have different file formats, such as ELF, PE or special formats for firmware images that are specifically crafted for a micro controller, which have to be parsed by a binary rewriter in order to access the contained information. While data that is contained in executable file formats, such as ELF and PE, can be grouped into two different data parts, namely administrative and payload, this is not necessarily true for firmware images that have been copied from en embedded system. The administrative data part usually provides further information about different sections that are contained in the binary. For ELF binaries the most important sections for the analysis step have been discussed in Subsection 2.2.1. Such administrative sections can also contain debug or type information, which can be used to help to recover more code more accurately in the analysis step. On the other hand, the contents of the payload section are often raw byte streams that can contain not only instructions, but also initialization data for global variables. If no debug information is attached to such a byte stream, the stream should be considered completely untyped, as no information is present on the location and the size of global variables or functions.

- **Analysis:** The purpose of the analysis step is to process the byte streams of instruction data from the previous step and recover as much of the programs control flow as possible. Depending on the strategy that is used by the binary rewriter, a simple disassembler might be sufficient, because a fully recovered control flow graph is not needed in the next steps. Instruction punning [23] can be seen as such an approach that would not need a fully recovered control flow graph to modify the binary, because in such a transformation a jump instruction is inserted in place of another instruction, which will then be copied over to the jump target with the code that should be executed. But if such a control flow graph, type or structural information is needed, then the use of a proper decompiler may be beneficial, otherwise a binary rewriter would have to implement such algorithms themselves. Recovering this type of information is not trivial, as the raw byte streams of instructions are completely agnostic to high-level constructs, such as data types, structures, unions or functions. A decompiler has to recover these from the semantics of the underlying instructions and then use the information to reconstruct as much useful higher-level code as possible.

- **Transformation**: After the binary has been analyzed, such that enough information for the transformation process is available, the transformation step can begin. In this step the binary rewriter starts to make changes to the control flow. Depending in the approach of the binary rewriter, these changes can be done by rewriting an instrumentation point, by changing a series of instructions in a

18

basic block or even by utilizing breakpoints, if the target system has support for such a feature [21]. Depending on how fine-grained a binary rewriter allows for a transformation to happen, other approaches have to be chosen, but it has to be minded that the more fine-grained a transformation process is, the more overhead will be encountered in the overall process.

**Code generation**: In the code generation step, the binary rewriter persists the changes in an executable form, the result of the code generation step is not necessarily the same for all different types of binary rewriters. For static binary rewriters such a form would be an executable binary in an appropriate file format. In most cases these formats will be ELF or PE files. Since an embedded systems utilize custom formats these formats have to be converted to another representation if the binary rewriter has no support for an appropriate file format that can be used by such an embedded system. To persist these changes, a binary rewriter could place the newly generated code into additional sections that contain all the transformed code, or utilize a memory patching algorithm to change the control flow direly after the binary has been loaded by the operating system. While the second approach leaves the original untouched an additional loader is needed for the changes to be applied. But also utilizing existing compilers to create a completely new binary is a possibility. Dynamic binary rewriters on the other hand, may not have the ability to persist the output of the transformation step, but therefore can use the generated code directly at runtime and execute it.

#### 3.2 Dynamic binary rewriter

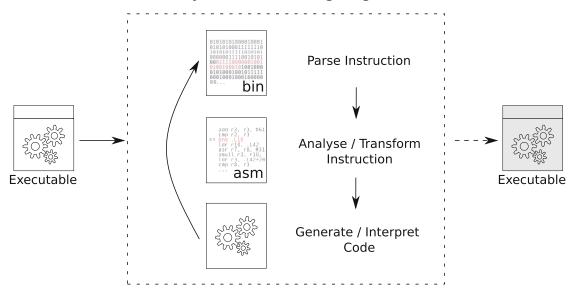

Dynamic binary rewriters manipulate the binary while it is executing and take advantage of the runtime information of the process. How such a dynamic binary rewriter can work is pictured in Figure 3.1. When the rewriting process is started, the binary is loaded into the memory, where the instructions can be transformed after the initial analysis step. There are multiple approaches how a dynamic binary rewriter can achieve this goal. For example, all instructions can be interpreted by the rewriting engine, which can lead to a higher overhead then with other methods. One other method would be to use breakpoints at locations where transformation has to take place or the control flow of the application has to be changed. For this approach a dynamic binary rewriter can try to attach itself in a similar fashion to the target binary like a debugger [5]. Depending on the dynamic binary rewriter, such an architecture can also be more sophisticated than in other cases. For example, Instrew [24] uses a client-server architecture to split the actual execution and code caching from the parsing, transformation and optimization. While this approach can be used in a very flexible manner, it can also cause noticeable runtime overhead, because all functions that are identified by the client process and are getting transformed by the server are transferred as ELF objects from one side to another. Since the rewriting process is performed by the server process, the client process has to cache received code in form of a code cache, which can speed up the execution time, but

**Dynamic Rewriting Engine**

Figure 3.1: Visualization of a dynamic binary rewriter process

requires a special execution manager that is able to prevent the program from executing unknown pieces of code [24]. Although this approach limits the analysis of the binary to the execution paths that it takes during the runtime, binaries, which try to obfuscate their code by utilizing unpacker and encrypted memory segments can be processed by a dynamic binary rewriter. BinRec [25] is also build with such a principle in mind, because the whole binary rewriting process is build upon the analysis of execution path that are taken by simulated inputs. But while not all inputs can reliably be recorded and relayed to the binary, such as network requests to live services, the rewriting process accounts for such missing inputs by providing incremental rewriting support. While a dynamic rewriting approach can handle such situations better than a static binary rewriter, it comes at the cost of a computing and memory overhead, as the analysis process and the patching process are performed at runtime [5]. Instrew and BinRec use the LLVM IR as intermediate representation for modifications before the binary gets compiled, other dynamic binary rewriter such as HERA [21] have a different approach. Since HERA is a specialized dynamic binary rewriter for embedded real time systems it has to take into account that the important scheduled tasks can be completed in real time. To allow for this, HERA uses the idle time of the processor to copy the patched code into a new memory region the hardware debugger functionality to install hardware breakpoints, such that the switch from the non-patched version can happen atomically. Instead of halting the execution of the task, HERA uses the debug functionality to automatically redirect the control flow to the patched code segment. A dynamic binary rewriter does not necessarily produce a patched binary that can be used after the rewriting process without the dynamic binary rewriter engine.

20

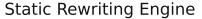

#### 3.3 Static binary rewriter

Figure 3.2: Visualization of a static binary rewriter process

In contrast to dynamic binary rewriter, static binary rewriter processes the binary by using static analysis, which means that the binary is most likely be processed as a while in each step before a patched output binary is produced, as shown in Figure 3.2. Static binary rewriters for ARM such as RevARM [26] or REPICA [27] use insertion-based approaches. In such an approach the code that is rewritten is inserted in the binary at the original location. This also means that if the rewritten code is bigger than the old one, all following direct and indirect jumps must be patched accordingly. While RevARM uses IDA Pro<sup>1</sup> for disassembling and creating the control flow graph, REPICA only uses the capstone<sup>2</sup> disassembler for preprocessing the binary. Although RevARM has a lower runtime overhead then other binary rewriters, dynamically generated, obfuscated or position independent code cannot be handled. Compared to other binary rewriters the overall space overhead that is introduced by the transformation of REPICA can be seen as negligible. But it does not seem to be suitable for firmware images for embedded systems, since it only focuses position independent android binaries and transforming other kinds of binaries might have undesired side effects. It has also been shown that inserting a shadow stack into the binary with REPICA can be done with less overhead than with Multiverse [27][28].

Instead of relying on a framework specific intermediate representation language, frameworks such as McSema [29] or Bin2llvm [30] lift the binaries directly to LLVM IR, which

<sup>&</sup>lt;sup>1</sup>https://www.hex-rays.com/products/ida/

<sup>&</sup>lt;sup>2</sup>https://www.capstone-engine.org/

then can be used to rewrite the binaries. But since lifting a binary into the LLVM IR is a very complex task, not all binaries can be processed since the lifting process is also not perfect and suffers from similar problems as it is the case with normal decompilers. Additionally, since the LLVM IR was built to support only compiler optimizations, an analysis of the binary in such a language can also be more troublesome than in an intermediate representation language that was built for such a task. But despite those shortcomings the binary rewriting process, fuzzing or even searching for vulnerabilities in such frameworks can be done in the LLVM IR [31]. This also eliminates the need to manually correct direct and indirect jumps, since the resulting code will be compiled by a compiler. While most modern binary analysis tools like IDA, Ghidra<sup>3</sup> or radare2<sup>4</sup> use an independent language to perform code analysis, compared to LLVM IR these other representations are only used for analysis and it is not supported that changes can be written back to assembly code [6]. Nevertheless, some solutions like RetroWrite [32] and SN4KE [33] utilize the features of such an intermediate representation language to perform instrumentation, fuzzing as well as mutation for binaries. SN4KE uses the GTIRB format, which is a high-level container that can store the structure of the binary in a format that can be processed by analysis and binary rewriting software. Additionally, to this feature, the original assembly is preserved, which makes it easier for insertion-based approaches to transform the binary while still being able to perform analysis of the control flow graph. But while GTIRB tries to encapsulate these important aspects for binary rewriters, a transformation into LLVM IR is still not trivially possible, because individual instruction still has to be transformed [34].

#### 3.4 LLVM IR binary rewriter

LLVM IR binary rewriter are dynamic or static binary rewriter that utilize the LLVM intermediate representation in their rewriting process and therefore must have the ability to transform the disassembled or decompiled program into this intermediate representation before it can be modified. This section will briefly describe how Instrew and McSema handle this process.

#### 3.4.1 Instrew

Since Instrew [24] is a dynamic binary rewriter, the binary is modified while it is being run, which means that the overall process of lifting, transforming and executing the newly generated code must be rather fast, otherwise the runtime performance will suffer from utilizing the framework. Besides basic modifications, also instrumentation is supported by Instrew and a client/server model is used in the transformation process. The server will be tasked to lift the assembly code, transform the lifted instructions to LLVM IR, apply the desired patches and compile back, such that the client can execute the newly generated code block. In this process the server process will first decode all instructions in a block,

<sup>&</sup>lt;sup>3</sup>https://ghidra-sre.org/

<sup>&</sup>lt;sup>4</sup>https://rada.re/n/

which means that from the current position of the program counter all instructions will be scanned linearly until a branching instruction is encountered, before attempting to transform the instructions. Then these decoded instructions are transformed to LLVM IR and if necessary  $\phi$ -expressions are generated before the generated code can be instrumented, changed or compiled. After the compilation, the compiled code segment is sent to the client progress, which starts to execute the code until a missing entry in the code cache is encountered.

#### 3.4.2 McSema

When a binary is rewritten with McSema, the binary is processed in two stages. In the first stage the binary will be analyzed and disassembled, which is done with the help of the Remill framework<sup>5</sup> and IDA Pro. This will generate a control flow graph with additional information for the next step. In this step the instructions will be lifted with the provided control flow into LLVM IR code. Compared to other binary rewriter, the transformation process of McSema uses a semantical approach where a series of instructions or even individual instructions are lifted as functions into the LLVM IR code. The implementation of these function can then vary depending on the target architecture and are often inlined in the compilation process to prevent the generation of additional overhead of a function call. Besides this the McSema binary rewriter will also create structures for handling the overall CPU and memory state of the application [29].

# CHAPTER 4

### Implementation

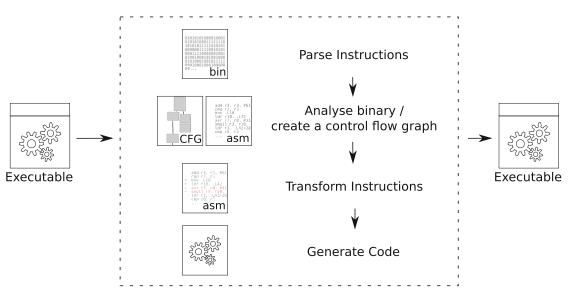

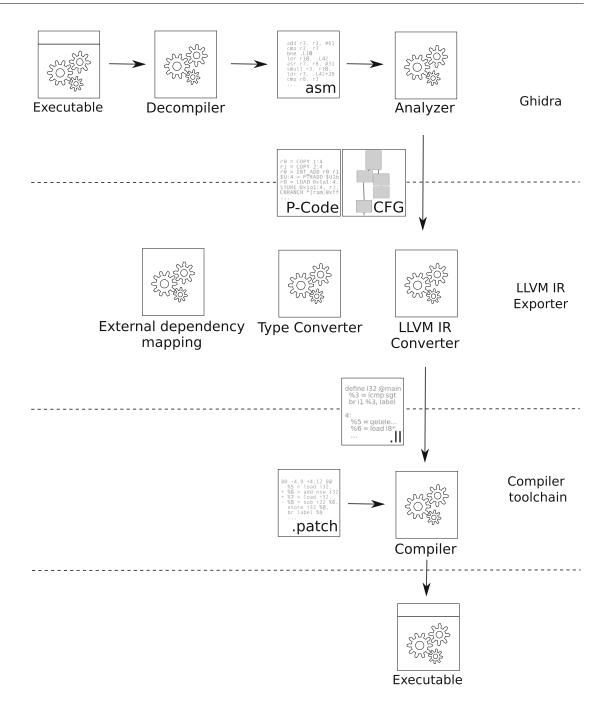

This chapter describes a rewriting approach that can be used to convert Ghidra's highlevel P-Code representation into LLVM IR. Figure 4.1 gives an overview of an example architecture of such a Ghidra plugin. The plugin does not only need the appropriate binaries as an input, but also the patchest and additional options, which can be used to customize the rewriting process. Such options are for example the different approaches to handle the linking of dynamically build binaries, as described in Section 4.9. While Ghidra provides a variety of different types of analyzers and binary parsers, a combination of them with different settings will produce different results and can impact the quality of the resulting transformation. But since the Ghidra plugin is encapsulated into a single action, also third-party analyzers can be used in Ghidra to improve the high-level P-Code representation. The resulting P-Code of the analyzing step is then used by the transformation step to convert the P-Code operations to LLVM IR expressions. Several issues must be addressed in this conversion, such as creating appropriate type information, handling stack variables, accounting for external dependencies, and more. This is because when P-Code operations are converted to LLVM IR expressions, not all P-code operations result in a single expression. Depending on the operations it can be zero or even multiple non-trival expressions. For example, a single COPY operation in P-Code copies the value from the input variable into the output variable. Such an operation can have multiple meanings in the LLVM IR environment, because depending on the used input other expressions as just an assignment operation may be needed. This is mostly the case, because P-Code does not distinguish between local or global symbols in the same way it is the case in LLVM. Although Ghidra represents global symbols as data labels and LLVM IR represents them as global pointers, many issues can arise when transforming different operations, which is discussed in more detail in Section 4.5. But also working with pointers and constant values can be a problem when transforming a binary, as absolute positions will most likely change during code generation, therefore additional measures have to be used to identify such constant pointer values. To improve detection

#### 4. Implementation

Figure 4.1: Overview of the binary rewriting process

of such values, the image base address can be changed to another higher address such as  $0 \times 0 \pm 50000$ . While this works great for position-independent binaries, the image base address of a system image used in an embedded device is important because the

**TU Bibliotheks** Die approbierte gedruckte Originalversion dieser Diplomarbeit ist an der TU Wien Bibliothek verfügbar WIEN Vourknowledge hub The approved original version of this thesis is available in print at TU Wien Bibliothek.

compiler may not have generated position-independent code and therefore moving the image base address will cause errors. Such errors can span from simple misidentification of data labels up to a completely different control flow. Additionally, it is important for embedded systems to note that the overall memory space is segmented into different areas and not all of these areas can contain program code. As a result, constant values that are used as pointers and reference an absolute position in the binary, can be easier distinguished from constant values that reference executable code and therefore can be identified correctly in the transformation process. The correct identification of types is very important as it will be discussed in Section 4.1.

| Ghidra type        | Size (in bytes)              | LLVM type                                 |

|--------------------|------------------------------|-------------------------------------------|

| void               | 0                            | void                                      |

| bool               | 1                            | i1                                        |

| char               | 1                            | i4                                        |

| short              | 2                            | i8                                        |

| int                | 4                            | i32                                       |

| long               | 8                            | i64                                       |

| float              | 4                            | £32                                       |

| double             | 8                            | f64                                       |

| Undefined          | size of (Undefined)          | i <size></size>                           |

| Array <t></t>      | n * size of(T)               | [n x T]                                   |

| Pointer <t></t>    | 4                            | Τ*                                        |

| Enumeration        | 4                            | i <size></size>                           |

| Structure          | sum(struct.elements)         | { <type list=""> }</type>                 |

| Union              | max(size of(union.elements)) | { <biggest type=""> }</biggest>           |

| FunctionDefinition | 4                            | ( <return> (<params>) *</params></return> |

| TypeDef <t></t>    | 0                            | Т                                         |

| String             | strlen(str)                  | [? x i8]                                  |

#### 4.1 Type Conversion

Table 4.1: Type Conversion

Converting types from P-Code to LLVM cannot be done trivially in all cases, because Ghidra tries to map all recognized types according to a simplified specification of the C/C++ language, as shown in Table 4.1. Therefore, not only primitive types such as int and char are present, but also type aliases (TypeDef) can exist, which has no representation in LLVM IR. This can partly be a problem, since such type constructs as TypeDef cannot be converted and integers have usually a platform depended size. Therefore, when converting types, the length of the individual types has to be considered. A great example for this behavior can be the Undefined data types, which can exist in different lengths and represent a type which Ghidra could not recover correctly. Most of the time such instances are limited to the size of a register and can therefore be safely converted to a native integer type, even if the full length is not needed in that instance. In other cases, the type could be bigger and represent a structure or a union type, which either has to be specified manually or an appropriate process has to be found to identify hand handle the type correctly. As a fallback method such a variable sized type can still be converted into a byte array. But when accessing such a type can be more difficult, as the types of the extracted members have to be casted to a compatible type.

As shown in Table 4.1 the sizes of types in Ghidra are given as bytes, while all types in LLVM IR are using bits to specify their length. Additionally, LLVM only specifies integer and floating-point types as primitive types, other type combinations such as char have to be mapped to an appropriate integer type in LLVM. When mapping such types, it is important to note, that while a char type in Ghidra has the length of one byte, the LLVM equivalent type would be i8, as all integer and floating-point types in LLVM specify their length in bits. Although it is possible to generate type structures in LLVM, the generation of these structures is not as simple as it seems. Dealing with structure and union types can be a bit more difficult, since these types can generally be constructed recursively and therefore a lazy approach must be taken. Such a behavior can be implemented with the LLVM API by first creating a named structure and then resolving all child types, as this ensures that a recursive reference to the same type can be resolved without producing an endless loop. Union types on the other hand, can be a problem, because LLVM does not directly support union types. To be able to handle such union types correctly a structure type should be defined with the length of the biggest containing element of the union [35]. To access the different elements of a union type, additional steps have to be performed as shown in Listing 5. Either a **bitcast** with an additional **load** expression has to be generated when accessing a component of a union, or alternatively also a **extractvalue** with an **trunc** could be used if the type can be casted to an array type.

```

; typedef union {

; char* ptr;

; long long lValue;

; } example;

;

; example->ptr

%union.example = type { i64 }

%1 = bitcast %union.example* %0 to i8**

%2 = load i8*, i8** %1, align 8

```

Listing 5: Example access of an union type in LLVM

When converting other higher-level types such as arrays and pointers the conversion from the Ghidra type to the LLVM IR type can be considered easier than it is the case with

**TU Bibliothek** Die approbierte gedruckte Originalversion dieser Diplomarbeit ist an der TU Wien Bibliothek verfügbar WIEN Your knowledge hub The approved original version of this thesis is available in print at TU Wien Bibliothek.

28

unions or structs, because these types cannot be specified in a in a recursive way without caching the declaration of the type in LLVM IR. For these types, which are denoted as TypeName<T> in Table 4.1, the containing type is T and has depending on the type different meanings. For arrays it is the type of the containing elements, for pointers it is the type which is pointed to and for type definitions it is the underlying type, which should be used instead of the type definition in LLVM IR. The type Enumeration is an enumeration type that Ghidra has recovered and has to be converted to the corresponding integer type when used in LLVM IR, since there is no support for such types in LLVM IR either. Similar to the C language, function definitions are function pointers that have both, a return type and parameters and therefore are converted in a similar fashion.

But not all types that are listed in Table 4.1 can easily be converted to their respective counterparts in LLVM. One of these types in a String data type in Ghidra. This datatype does not specify a length by itself and can only be converted to LLVM IR if the data is also known at the time of the conversion process. When converting the referenced data has to be queried and the length of the string has to be computed dynamically. Although this allows the creation of globally stored, or local string constants, working with these values is not trivial, because in most cases an implicit type cast is needed to convert a character array to a character pointer. Furthermore, it has to be noted that the existence of debug symbols can greatly increase the amount of complex types that can be recovered from the binary by Ghidra. If no such symbols are present most complex types will be represented as pointer operations in P-Code, which requires the generation of more complex typecasts, but may not require a sophisticated type conversion algorithm.

#### 4.2 Basic Blocks

When converting basic blocks from the control flow graph, note that the semantics between basic blocks from the high-level or low-level P-Code structure are different from the semantics of basic blocks in LLVM. In LLVM it is required that a block is terminated by a list of predefined instructions (terminator instructions), which is not always the case in the control flow graph structure provided by Ghidra [36]. Because of the default behavior in Ghidra, such terminator instructions are not needed, as the control flow will be implicitly transferred to the next block in the control flow graph, if only one child block exists. If no such trailing branch is found in the block, an implicit branching instruction (**br label** %NEXT\_BLOCK) has to be inserted at the end of the block where %NEXT\_BLOCK will be the label of the next block that is referenced in the control flow graph. In most cases a high-level P-Code block is terminated by a BRANCH, CBRANCH or BRANCHIND as the control flow branches at that position. High-level constructs such as loops, and branching statements (if, switch, goto) will produce such basic blocks and can therefore be detected by the decompiler when analyzing the control flow. While such blocks cannot only miss an explicit terminator instruction, these blocks can also contain a series of MULTIEQUAL operations that have to be handled with care, as explained in Section 4.8.1. The contents of Listing 6 can be seen as example of a series of blocks that do not contain these discussed terminator instructions and a MULTIEQUAL operation.

```

Ud080:1 = COPY (const, 0x1, 1)

CBRANCH * [ram] 0xff51026:8 , $Ud080:1

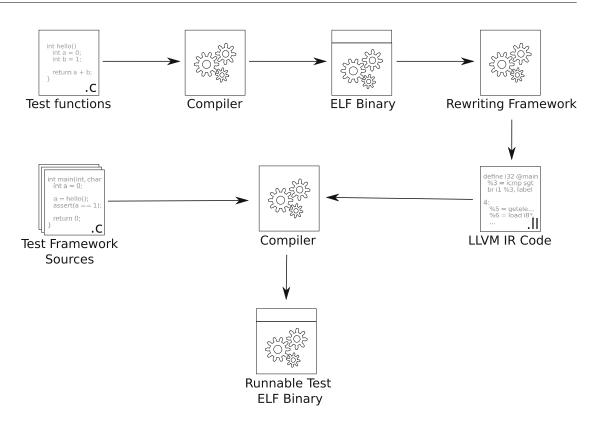

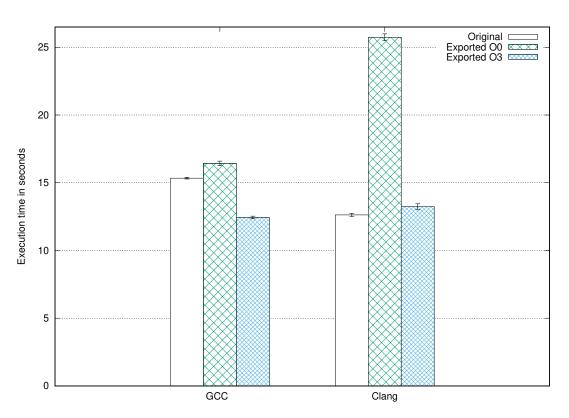

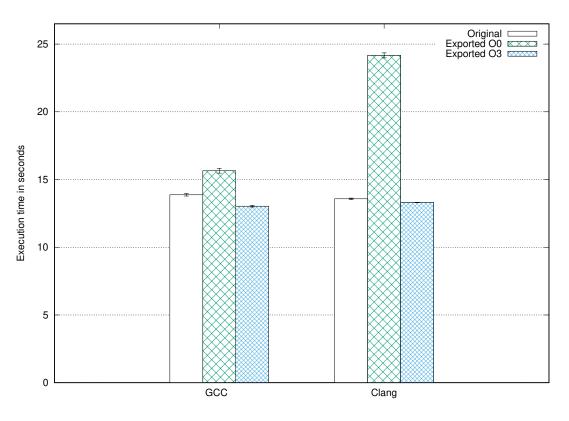

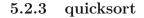

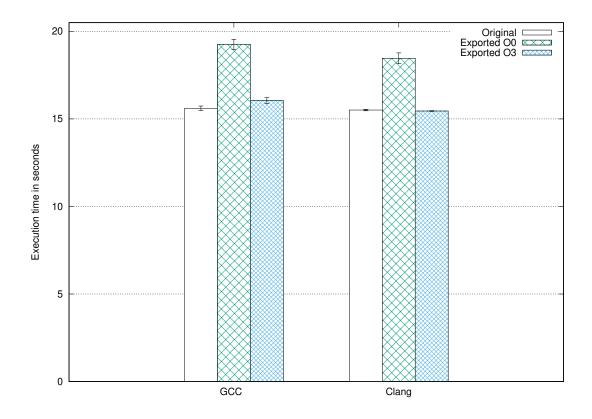

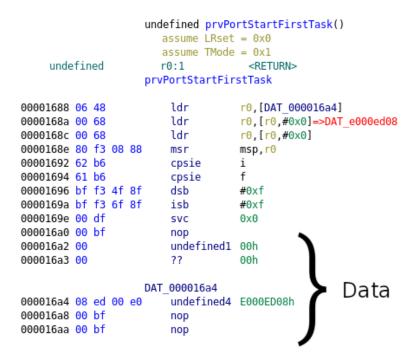

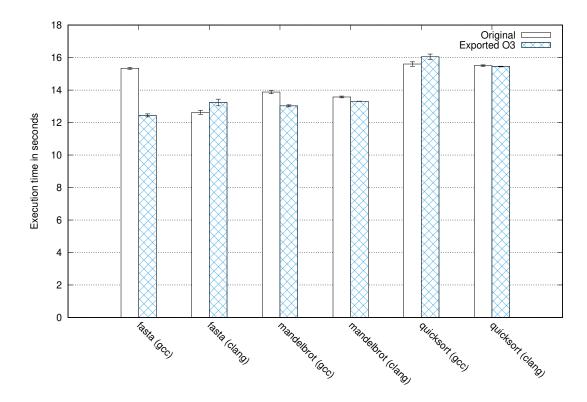

LAB 0ff51019: